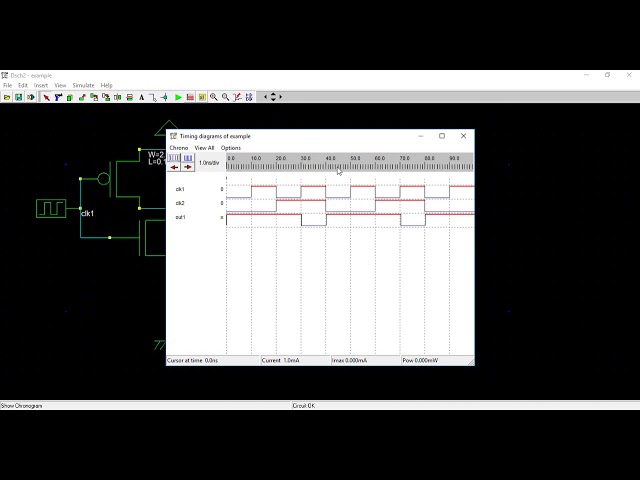

Vlsi Lab Cmos Inverter Using Dsch2 And Microwind 57 Off This video will tell you how to convert dsch2 schematic diagram to microwind layout. The cmos inverter layout was successfully designed and simulated using microwind. the output waveform demonstrates the correct inversion of the input signal. the logic high and low levels align with the expected characteristics of a cmos inverter. this experiment verified the.

Vlsi Lab Cmos Inverter Using Dsch2 And Microwind 57 Off Cmos inverter design using dsch and microwind softwaresdownload : microwind downloads. Enhanced document preview: lab no. 02 cmos 0.25 micron technology inverter characteristics and layout in microwind objective: in this lab, students will design and implement a cmos inverter. different design parameter's effects like transistor sizing, supply voltages, etc. will be analyzed and delay, area, power and current will be observed. Layout diagram of cmos inverter not gate: the diagram shown here is the stick diagram for the cmos inverter. it consists of a pmos and a nmos connected to get the inverted output. when the input is low, pmos (yellow) is on and pulls the output to vdd; hence it is called pull up device. Vlsi laboratory the students are required to design the schematic diagrams using cmos logic and to draw the layout diagrams to perform the following experiments using cmos 130nm technology with necessary eda tools (mentor graphics tanner). list of experiments: 1. design and implementation of an inverter 2.

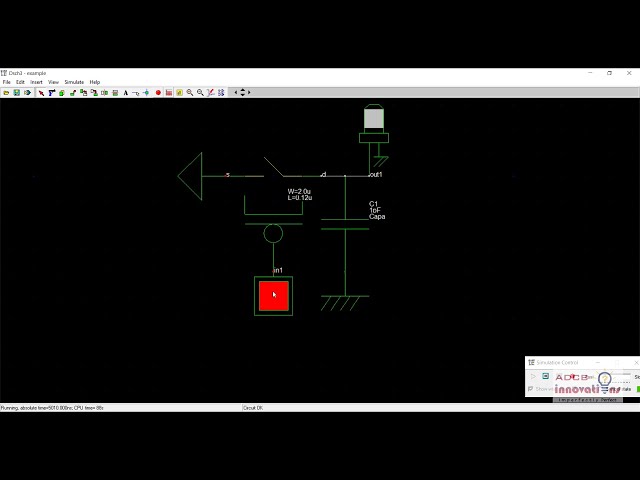

Vlsi Lab Cmos Inverter Using Dsch2 And Microwind 57 Off Layout diagram of cmos inverter not gate: the diagram shown here is the stick diagram for the cmos inverter. it consists of a pmos and a nmos connected to get the inverted output. when the input is low, pmos (yellow) is on and pulls the output to vdd; hence it is called pull up device. Vlsi laboratory the students are required to design the schematic diagrams using cmos logic and to draw the layout diagrams to perform the following experiments using cmos 130nm technology with necessary eda tools (mentor graphics tanner). list of experiments: 1. design and implementation of an inverter 2. Enhanced document preview: lab 3 layout extraction and simulation of a cmos inverter objective to draw the layout of a cmos inverter and buffer using dsch and microwind. tools required: microwind & dsch. lab task 1: cmos inverter: the nmos transistor and the pmos transistor form a typical complementary mos (cmos) device. The present paper introduces the design and simulation of cmos integrated circuits, in pc tools dsch and microwind version 2.6. which will helpful for users not only analysis of vlsi subject but also research and practical approach from circuit to simulation. This video is a part of vlsi lab and in previous video, cmos inverter is designed in dsch while in this video layout of the cmos inverter is designed. This lab assumed that students are familiar with microwind and lambda based design rules. the tool used in this lab is microwind. the tasks given in the lab include: design of cmos inverter and transistor sizing. layout design using the tool. gate delay, area, power and current analysis and the effects of transistor sizing on these parameters.

Lab2 Vlsi Pdf Cmos Mosfet Enhanced document preview: lab 3 layout extraction and simulation of a cmos inverter objective to draw the layout of a cmos inverter and buffer using dsch and microwind. tools required: microwind & dsch. lab task 1: cmos inverter: the nmos transistor and the pmos transistor form a typical complementary mos (cmos) device. The present paper introduces the design and simulation of cmos integrated circuits, in pc tools dsch and microwind version 2.6. which will helpful for users not only analysis of vlsi subject but also research and practical approach from circuit to simulation. This video is a part of vlsi lab and in previous video, cmos inverter is designed in dsch while in this video layout of the cmos inverter is designed. This lab assumed that students are familiar with microwind and lambda based design rules. the tool used in this lab is microwind. the tasks given in the lab include: design of cmos inverter and transistor sizing. layout design using the tool. gate delay, area, power and current analysis and the effects of transistor sizing on these parameters.